توضیحات

ABSTRACT

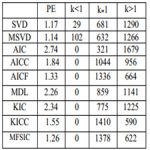

In this paper the capacitance components of the PSP compact model which is selected as successor of BSIM4 by the Compact Modelling Council (CMC) are investigated and simulated in HSPICE for the state of the art 35nm MOSFET device. The simulations are compared with TCAD results in both transcapacitance components between the device terminals and time domain to show the impact of accuracy of compact model on real circuit simulations.

INTRODUCTION

New ITRS 2008 update forecasts the scaling of bulk MOSFETs will be extended until 2016 . This makes a huge demand for better modelling of new generation of bulk MOSFETs with reduced gate length technologies, especially at sub-50nm technology nodes. Compact models are concise mathematical description of the complex device physics in the transistor. A compact model maintains a ne balance between the amount of detailed physics embedded for model accuracy and model compactness (computational efficiency). The simplications in the physics enable very fast analysis of device/circuit behaviour when compared to the much slower numerical based TCAD simulations. Compact models have been at the heart of EDA tools for over several decades, and are playing an ever increasingly important role in the nanometer system-on-chip era . In recent years, surface potential based compact models like PSP have attracted significant attention because of their better physical description of device characteristics compared to industry standard compact models like BSIM4 which is a threshold voltage based model. Threshold voltage based models like BSIM4 use fitting parameters to achieve continuity between weak and strong inversion and this is not based on physical description, and the accuracy of fitting varies from device to device. The surface potential based compact models have shown better continuity and smoothness in device behaviour especially in the transition from weak inversion to strong inversion.

چکیده

در این مقاله، اجزای خازنی مدل جمع و جور PSP که به عنوان جانشین BSIM4 توسط شورای مدل سازمانی (CMC) انتخاب شده است، در HSPICE برای وضعیت دستگاه های MOSFET 35nm مورد بررسی قرار گرفته و شبیه سازی شده است. شبیه سازی ها با نتایج TCAD در هر دو مؤلفه انتقال قدرت بین پایانه های دستگاه و دامنه زمان مقایسه شده است تا تاثیر دقت مدل جمع و جور بر روی شبیه سازی مدار واقعی را نشان دهد.

مقدمه

به روز رسانی جدید ITRS 2008 پیش بینی می کند که مقیاس MOSFET های فله تا سال 2016 افزایش یابد. این باعث می شود تقاضای زیادی برای مدل سازی بهتر نسل جدیدی از MOSFET های فله ای با تکنولوژی های کاهش طول دروازه بخصوص در گره های فن آوری زیر 50nm ایجاد شود. مدل های فشرده شرح مختصر ریاضی از فیزیک دستگاه پیچیده در ترانزیستور است. یک مدل جمع و جور، بین میزان فیزیک دقیق تعبیه شده برای دقت مدل و فشرده سازی مدل (بازده محاسباتی) بین توازن نهائی برقرار می شود. ساده سازی در فیزیک، تجزیه و تحلیل بسیار سریع رفتار دستگاه / مدار را در مقایسه با شبیه سازی های TCAD مبتنی بر عددی بسیار کند انجام می دهد. مدلهای کامپکتی در قلب ابزار EDA برای چندین دهه بوده و نقش مهمی را در سیستم عصبی نانومتری ایفا می کنند. در سال های اخیر، مدل های جمع و جور مبتنی بر پلت فرم سطح مانند PSP با توجه به توصیف فیزیکی آنها در مورد ویژگی های دستگاه در مقایسه با مدل های جامع استاندارد استاندارد مانند BSIM4 که یک مدل مبتنی بر آستانه مبتنی بر مدل هستند، توجه قابل توجهی را به خود جلب کرده است. مدل های مبتنی بر ولتاژ آستانه مانند BSIM4 از پارامترهای اتصالی برای دستیابی به تداوم بین تداخل ضعیف و قوی استفاده می کنند و این براساس توصیف فیزیکی نیست و دقت اتصالات از دستگاه به دستگاه متفاوت است. مدل های جمع و جور مبتنی بر پلت فرم مبتنی بر تداخل بهتر و صافی در رفتار دستگاه به ویژه در انتقال از ضعف ضعیف به چرخش قوی نشان داده شده است.

Year: 2010

Publisher : Eighteenth International Energy Conference of Iran

By : Daryoosh Dideban,Binjie Cheng, Negin Moezi, Xingsheng Wang, Asen Asenov

File Information: English Language/ 4 Page / size: 905 KB

سال :1389

ناشر : هجدهمین کنفرانس بین المللی برق ایران

کاری از : داریوش دلبن، بنجی چنگ، نگین معزی، Xingsheng Wang، اسن آسنوف

اطلاعات فایل : زبان انگلیسی / 4 صفحه / حجم : KB 905

![Evaluation of 35nm MOSFET Capacitance .[taliem.ir]](https://taliem.ir/wp-content/uploads/Evaluation-of-35nm-MOSFET-Capacitance-.taliem.ir_.jpg)

![Estimation of Simplified .[taliem.ir]](https://taliem.ir/wp-content/uploads/Estimation-of-Simplified-.taliem.ir_-150x150.jpg)

نقد و بررسیها

هنوز بررسیای ثبت نشده است.