توضیحات

ABSTRACT

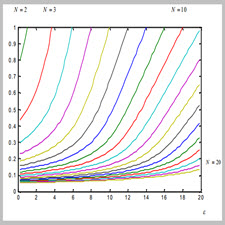

A set of low-power techniques is proposed to realize low power design in pipeline analog-to-digital converter (ADC). These techniques include removing the active S/H (i.e., SHA-less), sharing the opamp between the adjacent multi-bit-per-stages, low-power high-efficiency high-swing amplifier technique. Also, a new sampling topology is proposed to minimize aperture error by matching the time constant between the two input signal paths. All these skills are verified by simulation in the design of the 1.8-V 11-bit 40-MHz ADC in a 0.18-lm CMOS process with power dissipation 21-mW, signal-tonoise-and-distortion ratio (SNDR) 65-dB, effective number of bit (ENOB) 10.5-bit, spurious free dynamic range (SFDR) 78-dB, total harmonic distortion (THD) –75.4-dB, signal-to-noise ratio (SNR) 65.4-dB and figure-of-merit (FOM) 0.18 pJ/step.

INTRODUCTION

Low-power analog-to-digital converters (ADCs) with 10– 12-bit resolution and several tens of MHz sampling rates are recognized as one of the significant components in portable or battery-operated commercial applications including data communication and image signal processing systems. Recently, a lot of low-power technologies are proposed and verified in several designs. However, the time-interleaving architecture is easily limited by offset and gain mismatches as well as aperture errors between the interleaved channels. The performance of the pseudo-differential architecture compared with that of the fully differential one, is sensitive to the common mode voltage and substrate or power supply noise. Complex calibration schemes and/or circuit techniques, which are usually needed to enhance the linearity and/or correct the mismatches such as compensating low gain, low bandwidth and incomplete settling of opamps, need complicated algorithm, additional digital circuitry and extra calibration cycles. SHA-less and opamp-sharing are two important ways for low-power pipelined ADC design . However, they also bring some drawbacks affecting the ADC performance, such as nonlinearity and distortion. How to tradeoff and get rid of these bad factors are the hot points in the low-power Pipelined ADC design area. Reference takes use of dummy sampling capacitances and complicated digital calibration without opamp-sharing to enhance the SNR and SFDR performance.

چکیده

مجموعه ای از تکنیک های کم قدرت برای تحقق بخشیدن به طراحی کم توان در مبدل آنالوگ به دیجیتال (ADC) ارائه می شود. این تکنیکها شامل حذف S / H فعال (یعنی SHA کمتر)، به اشتراک گذاشتن opamp بین چند بیت برای هر مراحل مجاور، تکنولوژی تقویت کننده با قدرت بالا با راندمان بالا قدرت کم. همچنین، برای به حداقل رساندن خطای دیافراگم با تطبیق ثابت زمان بین دو مسیر سیگنال ورودی، یک توپولوژی نمونه برداری جدید پیشنهاد شده است. تمام این مهارت ها با شبیه سازی در طراحی الگوریتم AD-COS 11-بیتی 1.8 مگا پیکسل با فرکانس 0.18-lm CMOS با تخلیه قدرت 21 مگاوات، نسبت سیگنال و تحریف (SNDR) 65 dB ، تعداد قابل ملاحظهی بیت (ENOB) 10.5 بیتی، دامنه پویای آزاد فازی (SFDR) 78 dB، توازن هارمونیک توزیع (THD) -75.4 dB، نسبت سیگنال به نویز (SNR) 65.4 dB و رقم -merit (FOM) 0.18 pJ / step.

مقدمه

مبدلهای آنالوگ به دیجیتال (ADCs) با وضوح 10- 12 بیتی و چندین دهم فرکانس نمونه برداری MHz به عنوان یکی از اجزای مهم در کاربردهای تجاری قابل حمل یا باتری، از جمله سیستم های پردازش سیگنال و ارتباطات تصویر . به تازگی، بسیاری از تکنولوژی های کم قدرت در چندین طرح پیشنهادی و تایید شده اند. با این حال، معماری زمان interleaving به راحتی توسط اختلاط جبران شده و بدست آمده و همچنین اشتباهات دیافراگم بین کانال های میانبره محدود می شود. عملکرد معماری شبیه دیفرانسیل نسبت به آن کاملا متفاوت است، به ولتاژ معمولی حالت و سوکت یا سر و صدای منبع تغذیه حساس است. الگوریتم پیچیده، مدار دیجیتالی اضافی و چرخه های کالیبراسیون اضافی نیاز به برنامه های پیچیده کالیبراسیون و / یا تکنیک های مدار دارند که معمولا برای افزایش خطی بودن و یا اصلاح ناپیوستگی ها مانند جبران افزایش کم، پهنای باند کم و حل شدن ناقص اپین ها ضروری است. SHA-less و sharing opamp دو راه مهم برای طراحی ADC کم مصرف هستند. با این حال، آنها همچنین برخی از اشکالاتی را که بر عملکرد ADC تاثیر می گذارد، مانند عدم خطی بودن و تحریف. چگونگی خنثی کردن و خلاص شدن از این عوامل بد، نقاط داغ در منطقه طراحی ADC با اندازه کم توان است. مرجع با استفاده از ظرفیت نمونه برداری ساختگی و کالیبراسیون دیجیتالی پیچیده بدون به اشتراک گذاری opamp برای افزایش عملکرد SNR و SFDR استفاده می شود.

Year: 2012

Publisher : SPRINGER

By : Mingjun Fan , Junyan Ren , Ning Li, Fan Ye , Jun Xu

File Information: English Language/ 7 Page / size: 680 KB

Only site members can download free of charge after registering and adding to the cart

سال : 1391

ناشر : SPRINGER

کاری از : فن Mingjun، Junyan رن، نینگ لی، طرفدار یانگ، ژو ژو

اطلاعات فایل : زبان انگلیسی / 7 صفحه / حجم : KB 680

![Pipelined Analog-to-Digital converter (ADC)[taliem.ir]](https://taliem.ir/wp-content/uploads/Pipelined-Analog-to-Digital-converter-ADCtaliem.ir_.jpg)

![Probabilistic Modeling and Simulation of[taliem.ir]](https://taliem.ir/wp-content/uploads/Probabilistic-Modeling-and-Simulation-oftaliem.ir_-150x150.jpg)

![Study of Solar Energy Usage in Green Buildings[taliem.ir]](https://taliem.ir/wp-content/uploads/Study-of-Solar-Energy-Usage-in-Green-Buildingstaliem.ir_-150x150.jpg)

نقد و بررسیها

هنوز بررسیای ثبت نشده است.