توضیحات

ABSTRACT

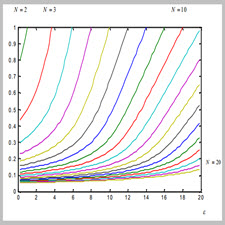

In this paper challenges observed in 65nm technology for circuits utilizing subthreshold region operation are presented. Different circuits are analyzed and simulated for ultra low supply voltages to find the best topology for subthreshold operation. To support the theoretical discussions different topologies are analyzed and simulated. Various aspects of flip-flop circuits are described in detail to study which topology would be most suitable for ultra low supply voltage and low-power applications. Simulation results show that the power consumption decreases by at least 23% compared with other flip-flops. Also, the setup time and the hold time are improved.

INTRODUCTION

In the last few years, large efforts have been made in research and development on low energy circuits for battery operated wireless sensor nodes. Recently a number of papers reporting ADC’s utilizing time-domain instead of amplitude domain have been reported . This class of converters may be built entirely of digital components, but this would put strict requirements on the comparator and sampling circuitry. To meet these requirements low power and high speed flip-flops with a sufficiently low possibility for metastability must be designed. Recently, as we approach atomic scale devices, leakage currents have increased dramatically, leading to higher static power dissipation. Therefore, leakage must be taken into consideration when evaluating these circuits since it has become a significant contributor to the overall power consumption in deepsubmicron CMOS processes Sub-threshold current rises due to lowering of threshold voltage which is scaled down to maintain transistor ON current in the face of falling power supply voltage. Voltage scaling for standby power reduction was suggested since both subthreshold current and gate current decrease dramatically (with V4 for gate leakage) . Lowering supply voltage thus saves standby power by decreasing both standby current and voltage . The subthreshold region (weak inversion) is often utilized to implement power efficient circuits for ultra low power wireless applications, but due to the much lower current in subthreshold region compared with higher supply voltages, the evaluation speed of such circuits operating in weak inversion is decreased. Therefore, new techniques to improve circuit speed need to be developed.

چکیده

در این مقاله چالش های موجود در فن آوری 65 نانومتر برای مدارهای با استفاده از عملیات منطقه زیرپوینت ارائه شده است. مدارهای مختلف برای ولتاژ های فوق العاده کم برای تخمین بهتر توپولوژی برای عملیات زیر عمل می کنند. برای حمایت از بحث های نظری، توپولوژی های مختلف تجزیه و تحلیل شده و شبیه سازی می شوند. جنبه های مختلف مدار مدار Flip-Flop به طور دقیق شرح داده شده است تا بتوانید کدام توپولوژی را برای ولتاژ بسیار کم ولتاژ و برنامه های کم قدرت مورد استفاده قرار دهید. نتایج شبیه سازی نشان می دهد که مصرف انرژی در مقایسه با دیگر فلیپ فلاپ ها، حداقل 23 درصد کاهش می یابد. همچنین زمان تنظیم و زمان نگهداری بهبود یافته است.

مقدمه

در چند سال گذشته، تلاش های زیادی در زمینه تحقیق و توسعه در مدارهای کم انرژی برای گره های حسگر بی سیم باتری انجام شده است. اخیرا تعداد مقالاتی مبنی بر استفاده از ADC در زمان دامنه به جای دامنه دامنه گزارش شده است. این کلاس مبدل ها می تواند به طور کامل از اجزای دیجیتال ساخته شده باشد، اما این الزامات سختگیرانه را در مدارهای مقایسه و نمونه گیری قرار می دهد. برای برآورده ساختن این نیازها، کمترین قدرت و فلیپ فلاپ با سرعت بالا با احتمال کمتری برای metastability باید طراحی شود. به تازگی، در حالیکه ما با دستگاههای مقیاس اتمی مقابله میکنیم، جریانهای نشتی به طور چشمگیری افزایش یافته و منجر به افزایش قدرت استاتیک میشود. بنابراین، هنگام ارزیابی این مدارها، نشت باید مورد توجه قرار گیرد، زیرا این ماده به میزان قابل توجهی از مصرف انرژی در فرآیندهای CMOS deepsubmicron تبدیل شده است. جریان زیر آستانه به دلیل کاهش ولتاژ آستانه ای که کاهش می یابد تا جریان ترانزیستور ON در صورت از ولتاژ منبع تغذیه کاهش می یابد. مقادیر ولتاژ برای کاهش توان آماده سازی پیشنهاد شد زیرا جریان جریان زیر و جریان دروازه به طور چشمگیری کاهش می یابد (با V4 برای نشت دروازه). کاهش ولتاژ منبع موجب صرفه جویی در مصرف انرژی در حالت آماده به کار می شود با کاهش هر دو جریان و ولتاژ آماده به کار. منطقه زیرپرونده (inversion ضعیف) اغلب برای اجرای مدارهای کارآمد برای برنامه های کاربردی بی سیم بسیار کم استفاده می شود، اما با توجه به جریان بسیار پایین در ناحیه زیر قطبی در مقایسه با ولتاژ های بالاتر، سرعت ارزیابی چنین مدارهایی که در معکوس ضعیف کاهش می یابد. بنابراین، تکنیک های جدید برای بهبود سرعت مدار باید توسعه یابد.

Year: 2009

Publisher : IEEE

By : Farshad Moradi , Dag T. Wisland , Hamid Mahmoodi , Ali Peiravi , Snorre Aunet, Tuan Vu Cao

File Information: English Language/ 5 Page / size: 722 KB

Only site members can download free of charge after registering and adding to the cart

سال : 1388

ناشر : IEEE

کاری از : فرشاد مرادی، دا ت. ویزند، حمید محمودی، علی پیروی، اسنوره عینت، توروو کائو

اطلاعات فایل : زبان انگلیسی / 5 صفحه / حجم : KB 722

![New Subthreshold Concepts in 65nm CMOS Technology[taliem.ir]](https://taliem.ir/wp-content/uploads/New-Subthreshold-Concepts-in-65nm-CMOS-Technologytaliem.ir_.jpg)

![Observer design for inherently nonlinear systems with lower triangular[taliem.ir]](https://taliem.ir/wp-content/uploads/Observer-design-for-inherently-nonlinear-systems-with-lower-triangulartaliem.ir_-150x150.jpg)

![Modelling and Fuzzy Control of DC Drive[taliem.ir]](https://taliem.ir/wp-content/uploads/Modelling-and-Fuzzy-Control-of-DC-Drivetaliem.ir_-1-150x150.jpg)

نقد و بررسیها

هنوز بررسیای ثبت نشده است.