توضیحات

ABSTRACT

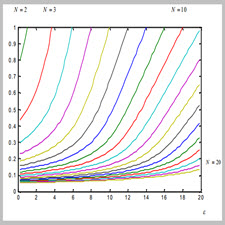

Input vector control (IVC) is a popular technique for leakage power reduction. It utilizes the transistor stack effect in CMOS gates by applying a minimum leakage vector (MLV) to the primary inputs of combinational circuits during the standby mode. However, the IVC technique becomes less effective for circuits of large logic depth because the input vector at primary inputs has little impact on leakage of internal gates at high logic levels. In this paper, we propose a technique to overcome this limitation by replacing those internal gates in their worst leakage states by other library gates while maintaining the circuit’s correct functionality during the active mode. This modification of the circuit does not require changes of the design flow, but it opens the door for further leakage reduction when the MLV is not effective. We then present a divide-and- conquer approach that integrates gate replacement, an optimal MLV searching algorithm for tree circuits, and a genetic algorithm to connect the tree circuits. Our experimental results on all the MCNC91 benchmark circuits reveal that 1) the gate replacement technique alone can achieve 10% leakage current reduction over the best known IVC methods with no delay penalty and little area increase; 2) the divide-and-conquer approach outperforms the best pure IVC method by 24% and the existing control point insertion method by 12%; and 3) compared with the leakage achieved by optimal MLV in small circuits, the gate replacement heuristic and the divide-and-conquer approach can reduce on average 13% and 17% leakage, respectively.

INTRODUCTION

AS THE VLSI technology and supply/threshold voltage continue scaling down, leakage power has become more and more significant in the power dissipation of today’s CMOS circuits. For example, it is projected that subthreshold leakage power can contribute as much as 42% of the total power in the 90-nm process generation . Many techniques thus have been proposed recently to reduce the leakage power consumption. Dual threshold voltage process uses devices with higher threshold voltage along noncritical paths to reduce leakage current while maintaining the performance . Multiple-threshold CMOS (MTCMOS) technique places a high device in series with low circuitry, creating a sleep transistor . In dynamic threshold MOS (DTMOS) , the gate and body are tied together and the threshold voltage is altered dynamically to suit the operating state of the circuit. Another technique to dynamically adjust threshold voltages is the variable threshold CMOS (VTCMOS) . All of these approaches require the process technology support.

چکیده

کنترل بردار ورودی (IVC) تکنیک محبوب برای کاهش قدرت نشت است. با استفاده از یک بردار حداقل نشت (MLV) به ورودی های اولیه مدارهای ترکیبی در حالت آماده به کار، از اثر ترانزیستور پشته در دروازه های CMOS استفاده می شود. با این حال، روش IVC برای مدارهای عمق منطقی بزرگ کمتر عمل می کند، زیرا بردار ورودی در ورودی های اولیه اثر کمی بر نشت دروازه های داخلی در سطوح منطقی بالا دارد. در این مقاله ما پیشنهاد می کنیم تکنیک برای غلبه بر این محدودیت با جایگزینی دروازه های داخلی در بدترین حالت های نشت توسط دروازه های کتابخانه دیگر، در حالی که حفظ عملکرد مدار صحیح در طول حالت فعال، پیشنهاد می شود. این اصلاح مدار نیازی به تغییر جریان طراحی نیست، اما برای کاهش بیشتر نشت زمانی که MLV موثر نیست، درب باز می شود. سپس یک رویکرد تقسیم و تسخیر ارائه می کنیم که جایگزینی دروازه، الگوریتم جستجوی مطلوب MLV برای مدارهای درختی و الگوریتم ژنتیکی برای اتصال مدارهای درونی را در نظر می گیرد. نتایج تجربی ما در تمام مدارهای MCNC91 نشان می دهد که 1) تکنیک جایگزینی دروازه می تواند به تنهایی 10 درصد کاهش جریان نشت را در بهترین روش های شناخته شده IVC بدون مجاز تاخیر و افزایش ناحیه کوچک به دست آورد. 2) روش تقسیم و تسخیر بهترین روش IVC خالص را 24٪ و روش Insert نقطه کنترول کنترلی را با 12٪ بهتر می کند؛ و 3) در مقایسه با نشتی که توسط MLV بهینه در مدارهای کوچک بدست می آید، اکتشاف جایگزین دروازه و رویکرد تقسیم و تسخیر می تواند به طور متوسط به میزان 13٪ و 17٪ نشت را کاهش دهد.

مقدمه

به عنوان فن آوری VLSI و عرضه / ولتاژ آستانه ادامه کاهش می یابد، قدرت نشت در تخریب قدرت مدارهای CMOS امروز تبدیل شده است. به عنوان مثال، پیش بینی شده است که قدرت نشت زیر قطر می تواند تا 42 درصد از کل قدرت در تولید نسل 90nm تولید کند. به تازگی پیشنهاد شده است که بسیاری از تکنیک ها برای کاهش مصرف برق نشتی پیشنهاد شده است. فرآیند ولتاژ آستانه دوگانه با استفاده از دستگاه هایی با ولتاژ آستانه بالاتر در امتداد مسیرهای غیر بحرانی برای کاهش جریان نشت در حالی که عملکرد را حفظ می کند. تکنیک CMOS با چندین آستانه (MTCMOS) یک دستگاه بالاتری را با سری مدارهای کم و یک ترانزیستور خواب ایجاد می کند. در آستانه پویا MOS (DTMOS)، دروازه و بدن با هم گره خورده و ولتاژ آستانه به طور پویا تغییر می کند تا با حالت عملیاتی مدار منطبق شود. یک روش دیگر برای تنظیم ولتاژ آستانه به صورت پویا آستانه متغیر CMOS (VTCMOS) است. همه این رویکردها نیاز به حمایت فن آوری فرایند دارند.

Year: 2006

Publisher : IEEE

By : Lin Yuan and Gang Qu

File Information: English Language/ 10 Page / size: 470 KB

Only site members can download free of charge after registering and adding to the cart

سال : 1385

ناشر : IEEE

کاری از : لین Yuan و Gang Qu

اطلاعات فایل : زبان انگلیسی / 10 صفحه / حجم : KB 470

![A Combined Gate Replacement and Input Vector[taliem.ir]](https://taliem.ir/wp-content/uploads/A-Combined-Gate-Replacement-and-Input-Vectortaliem.ir_.jpg)

![A Novel Hybrid Network Architecture to Increase[taliem.ir]](https://taliem.ir/wp-content/uploads/A-Novel-Hybrid-Network-Architecture-to-Increasetaliem.ir_-150x150.jpg)

![Advanced Control Architectures for Intelligent[taliem.ir]](https://taliem.ir/wp-content/uploads/Advanced-Control-Architectures-for-Intelligenttaliem.ir_-150x150.jpg)

نقد و بررسیها

هنوز بررسیای ثبت نشده است.